How do you see the waveform in Xilinx ISE?

How do you see the waveform in Xilinx ISE?

Note: Currently you cannot view the waveform by selecting “File -> Open” and then the . wdb file directly in ISE Simulator GUI. Running the command line is the only way to view the waveform.

How do you run simulation in Xilinx ISE?

To run the simulation in ISE Simulator, click on the test fixture in the Sources window to highlight it, expand the Xilinx ISE Simulator option in the Processes window, and double-click Simulate Behavioral Model. ModelSim will open and run the test code in your test fixture file.

What is ISIM Xilinx?

ISim is an abbreviation for ISE Simulator, an integrated HDL simulator used to simulate Xilinx FPGA and CPLD designs.

How do you write Verilog code in Xilinx ISE?

To prepare a Verilog module for integration into LabVIEW FPGA, you must first create a project and configure it properly in the Xilinx ISE Design Suite.

- Open Xilinx ISE Design Suite from Start » All Programs » Xilinx ISE.

- Click File » New Project and configure the Create New Project page as shown below.

How do I run in Xilinx?

Executing a Run Configuration

- Click Run > Run Configurations.

- Select an existing run configuration in the Configurations list.

- Click Run.

- SDK downloads and executes the program on the target.

- To view the program output, use the STDIO Connection tab to use SDK console.

How Verilog code is executed?

A nonblocking assignment executes in two steps. First, it samples the values of the right-side variables. Then it updates the values to the left-side variables. The sampling step of a nonblocking assignment is an active event and thus is executed at the moment the nonblocking statement is encountered.

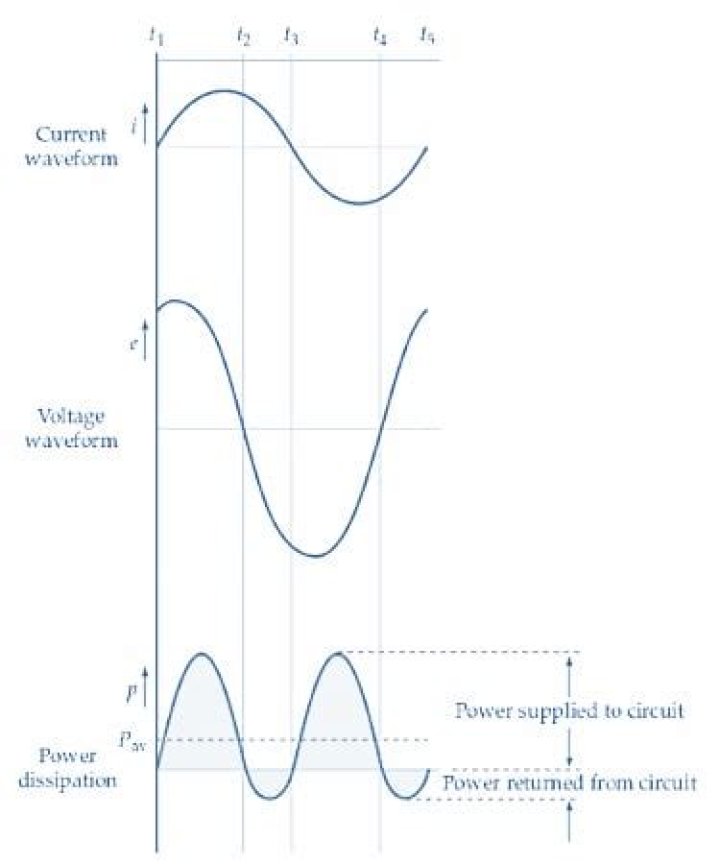

What is a Verilog simulator?

Verilog is a hardware description language and there is no requirement for designers to simulate their RTL designs to be able to convert them into logic gates. Simulation allows us to view the timing diagram of related signals to understand how the design description in Verilog actually behaves. …